#### МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

федеральное государственное бюджетное образовательное учреждение высшего образования

«Тольяттинский государственный университет»

#### ИНСТИТУТ ЭНЕРГЕТИКИ И ЭЛЕКТРОТЕХНИКИ

(институт)

Промышленная электроника (кафедра)

11.03.04 Электроника и наноэлектроника

(код и наименование направления подготовки, специальности)

Промышленная электроника

(направленность (профиль)/специализация)

#### БАКАЛАВРСКАЯ РАБОТА

на тему ЭЛЕКТРОННЫЙ МОДУЛЬ ТЕСТИРОВАНИЯ ОСНОВНЫХ КОМПОНЕНТОВ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ

| Студент(ка)     | А.С. Сураев                                                                    |                  |  |  |

|-----------------|--------------------------------------------------------------------------------|------------------|--|--|

| Руководитель    | (И.О. Фамилия)<br>к.т.н., доцент В.А. Медведев                                 | (личная подпись) |  |  |

|                 | (И.О. Фамилия)                                                                 | (личная подпись) |  |  |

|                 |                                                                                |                  |  |  |

| Допустить к заш | ците                                                                           |                  |  |  |

| Заведующий кафо | едрой <u>к.т.н., доцент А.А. Шевцов</u> (ученая степень, звание, И.О. Фамилия) | (личная подпись) |  |  |

| « »             | 20 г.                                                                          | (личная подпись) |  |  |

#### Аннотация

УДК 621.314.572 ББК 32 852

Бакалаврская работа Сураева Александра Сергеевича по теме «Электронный модуль тестирования основных компонентов микропроцессорной системы». Руководитель: Медведев Валерий Александрович. Защищена в Тольяттинском государственном университете в 2018 году.

Пояснительная записка: 62с., 3 разд., 39 рис. прил. 20с.

Графическая часть - 6 листов формата А1.

Ключевые слова: модуль тестирования, тестирование оборудования, разбраковка микропроцессоров, неразрушающее тестирование памяти, программное обеспечение, микропроцессор, характеристики канала связи, алгоритм работы модуля, печатная плата, эксплуатационная документация.

Бакалаврская работа посвящена разработке электронного модуля тестирования основных компонентов микропроцессорной системы. В ходе проектирования модуля разработана его структурная схема, дано обоснование выбора элементной базы, разработаны принципиальная схема и печатная плата модуля тестирования. Выбраны средства программирования и отладки микроконтроллера.

# Содержание

| Введение                                                  | 5            |

|-----------------------------------------------------------|--------------|

| 1 Анализ основных особенностей работы модуля тестирования | компонентов  |

| микропроцессорной системы                                 | 7            |

| 1.1 Анализ основных проблем тестирования оборудования     | 7            |

| 1.2 Особенности применения аппаратуры тестирования и      | разбраковки  |

| микропроцессоров                                          | 8            |

| 1.2.1 Первоначальная отладка                              | 8            |

| 1.2.2 Тестирование микросхем                              | 9            |

| 1.2.3 Разбраковка                                         | 10           |

| 1.2.4 Оценка эффективности применения аппаратуры          | 10           |

| 1.2.5 Маршрут разработки аппаратуры тестирования          | 11           |

| 1.3 Обзор методов тестирования оперативной памяти         | 14           |

| 1.3.1 Неразрушающее тестирование памяти                   | 16           |

| 1.3.2 Тестирование по методу Николаидиса                  | 18           |

| 1.4 Требования к разрабатываемому модулю                  | 21           |

| 2 Проектирование микропроцессорного модуля тестирования   | 22           |

| 2.1 Проектирование архитектуры модуля тестирования        | компонентов  |

| микропроцессорной системы                                 | 22           |

| 2.2 Выбор аппаратного и программного обеспечения          | 24           |

| 2.2.1 Выбор компонентов модуля тестирования               | компонентов  |

| микропроцессорной системы                                 | 24           |

| 2.2.2 Выбор программного обеспечения                      | 35           |

| 2.2.3 Технические характеристики каналов связи между пр   | роектируемым |

| устройством и тестируемым устройством                     |              |

| 2.3 Алгоритм работы микропроцессорной системы             | 41           |

| 2   | 2.4   | Методы     | обеспечения    | качества   | модуля    | тестирования       | компонентов |

|-----|-------|------------|----------------|------------|-----------|--------------------|-------------|

| N   | иикр  | опроцесс   | орной системь  | I          | •••••     |                    | 41          |

| 3 P | еалі  | изация ми  | кропроцессорь  | юго модул  | я тестиро | вания              | 46          |

| 3   | 3.1 F | Сонструкт  | орско-техноло  | гическая д | окумента  | ция системы        | 46          |

|     | 3.    | 1.1 Описа  | ние процесса и | зготовлени | ия печатн | ой платы           | 46          |

|     |       | •          | •              |            | •         | ля тестировани<br> |             |

|     |       |            |                |            | _         | ания модуля        | _           |

|     |       |            |                |            |           | о модуля тестир    |             |

|     |       |            | -              | •          |           | микропроцессо      | -           |

|     |       |            |                |            |           |                    |             |

| Спі | исоі  | к использу | уемой литепату | ⁄ры        |           |                    | 64          |

#### Введение

Проверка микропроцессорной системы заключается в исследовании ее работоспособности, с использованием специализированных программно ориентированных или внутрисхемно ориентированных устройств тестирования. Тестирование обычно происходит на стадиях разработки и починки микропроцессорной системы. Также проверку системы проводят при ее эксплуатации, для проверок на наличие ошибок и достоверности обработки данных.

Универсальность и гибкость микропроцессорных систем (МПС), как устройств с программным управлением наряду с высокой надежностью и дешевизной позволяют широко применять их в самых различных системах управления для замены аппаратной реализации функций управления, контроля, измерения и обработки данных. Микропроцессорные средства позволяют создавать разнообразные по сложности выполняемых функций устройства управления — от простейших микроконтроллеров несложных приборов и механизмов до сложнейших специализированных и универсальных систем распределенного управления в реальном времени.

Довольно часто в процессе тестирования и эксплуатации различных электронных и микропроцессорных систем возникает необходимость в некотором устройстве, с помощью которого можно было бы отображать тестовую и другую информацию и управлять этими системами. В роли такого устройства целесообразно использовать малогабаритный электронный блок, способный обмениваться с внешними устройствами по последовательному каналу. Если же блок содержит в себе микропроцессор, он становится универсальным средством, способным работать с любыми протоколами и даже выступать в качестве самостоятельного автономного программируемого устройства управления и контроля.

**Цель бакалаврской работы:** разработать модуль, способный универсальным образом подключаться к электронному или микропроцессорному устройству для его контроля. **Объектом исследования** являются микропроцессоры, постоянная память и устройства ввода-вывода, применяемые при тестировании и эксплуатации электронных устройств.

# 1 Анализ основных особенностей работы модуля тестирования компонентов микропроцессорной системы

#### 1.1 Анализ основных проблем тестирования оборудования

При применении цифровых вычислительных систем возникают уникальные проблемы поиска неисправностей, это вызвано особенностями их организации и структуры. Все компоненты в электронных системах отказывают по различным причинам, что может привести к частичному либо полному выходу вычислительной системы из строя.

Архитектура микропроцессорной системы зачастую делает процедуру поиска неисправного компонента в сложной и длительной. По мере все большего увеличения элементов в платах проблемы их функционального тестирования резко усложняются. Любые электронные системы тестируются лишь от части, а отказы могут проявится при эксплуатации при применении тех комбинаций сигналов, которые не были проанализированы во время тестирования, либо установке таких параметров компонентов системы, которые могут вызывать нехарактерное поведение микросхемы.

Правильность работы микропроцессорной системы задает требования использования исправных аппаратных средств и безошибочного программного обеспечения. Зачастую программы считающиеся целиком работоспособными, в некоторых случаях могут показывать неверные результаты. Программа может функционировать верно на тестовых наборах, но не работать при эксплуатации из-за наличия непредвиденного набора кода, который она не в состоянии обработать. Эти ситуации проявляются в программах, которые в следствии плохой конструкции не допускают ввод информации не опытным оператором, что приводит к мнимому отказу системы.

Отказы системы также возникают после некоторого срока эксплуатации системы, это связанно с неисправностью компонентов либо, гораздо реже, программными отказами из-за искажения хранимых данных в памяти кодов команд.

# 1.2 Особенности применения аппаратуры тестирования и разбраковки микропроцессоров

Тестирование и разбраковка, следующие за первоначальной отладкой, являются завершающими этапами в создании новой модели микропроцессора, успешная постановка которых определяет и успех процесса в целом. Они в решающей степени зависят от наличия специализированной аппаратуры, обеспечивающей всесторонний и детальный контроль конечного изделия в заданных режимах работы.

#### 1.2.1 Первоначальная отладка

После изготовления опытной партии микросхем проводится первоначальная отладка, выявляющая дефекты микросхем и позволяющая найти их программные и аппаратные обходы. Этим обеспечивается устойчивое функционирование изделия для дальнейшей работы с ним.

На этапе отладки микросхемы в первую очередь могут возникнуть следующие проблемы:

- а) выявление внутренних неисправностей микропроцессора, связанных с физическим проектированием;

- б) необходимость найти диапазоны устойчивой работоспособности внешних каналов микросхемы, таких как каналы оперативной памяти, вводавывода и межпроцессорных обменов.

Именно ошибки подобного рода вызывают большие трудности с их локализацией.

Как правило, неисправности приводят к нестабильной работоспособности некоторых или всех блоков в зависимости от внешних параметров, таких как напряжение питания, частота синхросигнала, температура. О неверном функционировании физических структур можно либо косвенно догадываться по некорректной работе блоков, либо использовать более скудные средства для измерений по сравнению с инструментами анализа логических ошибок. Например, ошибка в задании временного ограничения одного из сигналов при физи-

ческом проектировании блока микропроцессора может приводить к нестабильным сбоям при записи данных в регистровый файл из памяти. Сбои могут возникать в определенном диапазоне частоты синхросигнала, который зависит от напряжения питания и внутренней температуры микросхемы. Помочь в локализации неисправности могут как встроенные средства анализа логических сигналов в микропроцессоре, так и эксперименты с изменением частоты, и напряжения питания.

Проблему с системой распределения напряжения питания внутри микропроцессора могут помочь обнаружить тестовые выходы микросхемы, с помощью которых, используя осциллограф, можно зафиксировать изменения внутреннего напряжения питания во времени.

В стенде, на котором ведется первоначальная отладка, важно иметь такие средства, как возможность плавной регулировки частоты системных синхросигналов и напряжения питания, настройки внутренних параметров микропроцессора через контакты, а также возможность проводить измерения на внешних выводах микросхемы, как тестовых, так и сигнальных.

#### 1.2.2 Тестирование микросхем

Первоначальная отладка завершается после успешного прогона базовых пакетов тестов, после чего начинается процесс тестирования, в ходе которого в заявленных условиях выполняются проверка работоспособности (корректности функционирования всех узлов микросхемы) и соответствие микросхемы требуемым характеристикам производительности, потребляемой мощности, надежности и прочим.

С одной стороны, тестирование необходимо провести быстрее для уменьшения времени выхода конечного продукта, с другой — тестирование должно иметь широкое покрытие для более точного определения отсутствия неисправностей. Чтобы выполнить эти условия, используются специальные аппаратура и программное обеспечение, позволяющие:

а) создать наиболее полную конфигурацию для проверки всех функциональных блоков во всех режимах;

б) использовать достаточный объем программных диагностических средств для гибкого изменения внешних параметров, удобства и сокращения времени поиска причин неисправностей.

#### 1.2.3 Разбраковка

По окончании тестирования принимается решение об исправлении найденных ошибок и начале промышленного производства микропроцессоров. Полученные с фабрики микросхемы перед использованием по назначению проходят процесс разбраковки, а именно проверку на отсутствие неисправностей, связанных с дефектами изготовления. В отличие от тестирования в этом процессе выявляется более узкий спектр неисправностей, но действуют достаточно жесткие ограничения по времени. Анализ требований к процессу разбраковки показал, что в этом случае целесообразно использовать то же оборудование, что и для тестирования, но с запуском компактного пакета тестов, направленных на обнаружение дефектов производства.

#### 1.2.4 Оценка эффективности применения аппаратуры

Недостаточное количество имеющихся в наличии стендов для тестирования может привести к ограничениям по вариативности и параллельности тестирования. Эти проблемы возникают из-за необходимости проверять микропроцессор в областях заложенной микроархитектуры и топологии кристалла, а также печатные платы и корпус, используя модули стенда, позволяющие реализовать различные параметры и режимы работы.

После выявления работоспособного микропроцессора необходимо запускать тестирование операционной системы, программы начального старта, бинарного компилятора и различных приложений. Ввиду большого объема тестируемого программного обеспечения для этого необходимо иметь несколько машин.

Наличие USB-канала инженерного потокового тестирования микропроцессора позволяет снизить трудоемкость локализации ошибок в микропроцессоре.

Для исследования причин ошибок применяются два независимых кон-

троллера JTAG и две независимых консоли.

Активно используется регулировка уровней напряжения на источниках питания и рабочих частот микропроцессора.

#### 1.2.5 Маршрут разработки аппаратуры тестирования

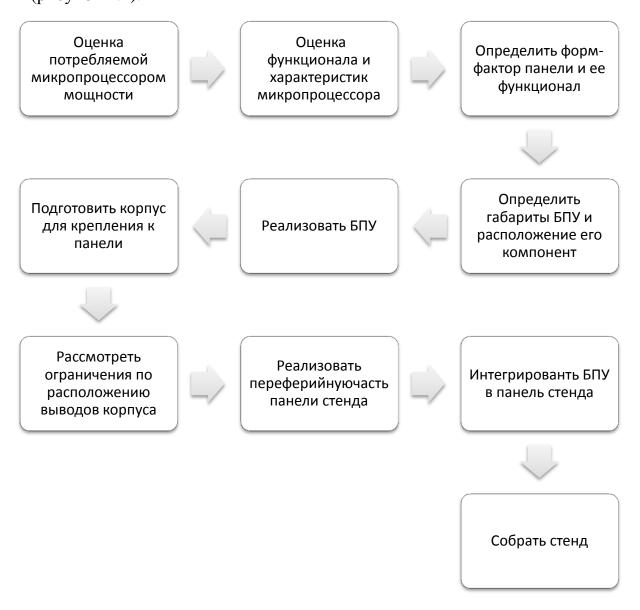

Как показано на схеме, приведенной на рисунке 1.1, проектирование стенда для тестирования микропроцессора начинается на этапе планирования кристалла микропроцессора, продолжается параллельно с разработкой корпуса и напрямую увязано с ее результатами. Основными данными выступают габариты корпуса и назначение сигналов на матрице выводов, оценка потребляемой мощности микропроцессора и подлежащие проверке функциональные возможности микропроцессора.

Рисунок 1.1 – Схема зависимости задач проектирования стенда тестирования от задач проектирования микропроцессора

Определяющими параметрами при этом являются:

- а) сведенные к минимуму размеры и количество слоев печатной платы стенда, равномерное их заполнение проводниками;

- б) физические размеры компонентов стенда, предусматриваемых к применению с проектируемым микропроцессором исходя из его функциональных возможностей;

- в) назначение сигналов на выводах связанных с микропроцессором ком-

понентов и взаимное расположение последних;

г) минимизация падения напряжения и перекосов по питанию на пути вдоль корпуса микросхемы.

Для определения приведенных выше параметров необходимо провести проектирование вычислительной панели, обеспечивающей выполне-

ние большей части задач тестирования и разбраковки микропроцессора (рисунок 1.2).

Рисунок 1.2 – Последовательность проектирования стенда для тестирования микропроцессоров.

Чтобы максимально унифицировать однотипные элементы панели, она разрабатывается с применением блоков процессорных

унифицированных (БПУ). БПУ включает:

- а) фрагмент печатной платы, содержащий микропроцессор;

- б) сокеты каналов оперативной памяти;

- в) набор последовательных конденсаторов, размещенных на линиях передатчиков высокоскоростного канала взаимодействия с контроллером периферийных интерфейсов КПИ-2, который реализован на интерфейсе IOWLink;

- г) три набора конденсаторов, размещенных на линиях передатчиков высокоскоростных межпроцессорных каналов взаимодействия IPLink (A, B, C);

- д) генераторы синхросигналов, обеспечивающих подачу опорной частоты микропроцессора;

- е) микропереключатели служебными для управления сигналами предназначенными управления заданием количества ДЛЯ процессорных ядер частоты высокоскоростного канала взаимодействия контроллером периферийного интерфейса;

- ж) систему питания.

Проектирование БПУ является весьма трудоемкой задачей И занимает большую часть времени разработки стенда. По завершении проектирова-БПУ становится законченным изделием, представляемым ния В вибиблиотечного де элемента. Он может быть тиражирован как в этом, так и в любом другом из де-

лии. Причем при условии резервирования необходимого места на пан ели интегрирование происходит достаточно быстро.

С помощью стендов для тестирования и разбраковки новых моделей микропроцессоров интегрально проверяется функцио нирование всех элементов микропроцессоров в различных режимах работы.

#### 1.3 Обзор методов тестирования оперативной памяти

В настоящее время быстро прогрессирующие технологии производства полупроводниковых приборов позволяют создавать схемы ОЗУ с чрезвычайно высокой степенью интеграции.

Нежелательным последствием использования новых технологий является увеличение вероятности возникновения неисправностей. Для обеспечения надежного функционирования цифровых систем большое внимание должно быть уделено своевременному обнаружению неисправностей памяти, поскольку результаты исследований свидетельствуют о том, что отказы ОЗУ могут составлять до 70% от общего числа отказов системы в целом.

Помимо традиционного заводского контроля на этапе производства в настоящее время широко применяется встроенная аппаратура самотестирования ВАСТ . Такой подход позволяет периодически выполнять тестирование на внутренней частоте без применения внешнего оборудования. Большинство ВАСТ реализуют тесты сложности O(N) (N – емкость запоминающего устройства), называемые маршевыми тестами .

При выполнении стандартного маршевого тестирования со всеми ячейками памяти в определенном порядке (↑ — от младших адресов к старшим, ↓ — наоборот, ↑ — в любом направлении) выполняются операции, задаваемые несколькими маршевыми элементами. Используются операции: w0, w1 — запись в элемент памяти значений 0 или 1; r0, r1 — чтение текущего значения из элемента памяти и сравнение его со значением 0 или 1.

Достоинствами маршевых тестов являются относительно высокие скорость выполнения и покрывающая способность, а также простота реализации ВАСТ. Из недостатков можно отметить полную потерю хранящейся в памяти информации после выполнения тестирования, что ограничивает применение классических маршевых тестов только моментами начального тестирования устройства.

Для надежной работы постоянно включенных систем, помимо методов с использованием избыточных данных (коды Хэмминга, контроль на четность), применяются методы периодического неразрушающего тестирования, основанного на классических маршевых алгоритмах.

При анализе покрывающей способности маршевых тестов рассматриваются не реальные дефекты в структуре ОЗУ (замыкания, обрывы и т.п.), а математические модели, описывающие функциональное проявление этих дефектов в процессе работы памяти. На рисунок 1.3 представлены наиболее распространенные модели неисправностей.

Константные неисправности (Stuck-At Fault — SAF)

•Логическое значение ячейки памяти всегда равно 0 (SA0) или 1 (SA1) независимо от операций, производимой с этой или другими ячейками памяти

Переходная неисправность (Transition Fault — TF)

•Ячейка не способна осуществлять переход из состояния логического 0 в состояние логической 1 (TF↑) либо наоборот (TF↓)

Неисправности взаимного влияния (Coupling Fault — CF)

- •Инверсная неисправность CF (Inversion CF CFin). Изменение значения влияющей ячейки вызывает инвертирование значения зависимой. Возможны следующие виды неисправностей CFin:  $\Lambda(\uparrow, \updownarrow)$ ,  $\Lambda(\downarrow, \updownarrow)$ ,  $V(\uparrow, \updownarrow)$ ,  $V(\downarrow, \updownarrow)$

- •Неинверсная неисправность CF (Idempotent CF CFid). Изменение значения влияющей ячейки переводит зависимую ячейку в определенное состояние. Возможно восемь видов неисправностей CFid:  $\Lambda(\uparrow,0)$ ,  $\Lambda(\uparrow,1)$ ,  $\Lambda(\downarrow,0)$ ,  $\Lambda(\downarrow,1)$ ,  $V(\uparrow,0)$ ,  $V(\uparrow,1)$ ,  $V(\downarrow,0)$ ,  $V(\downarrow,1)$

- •Константная неисправность CF (State CF CFst). Переход зависимой ячейки в какое-либо состояние возможен только при определенном значении влияющей ячейки. Различают следующие неисправности CFst:  $\Lambda(0,0)$ ,  $\Lambda(0,1)$ ,  $\Lambda(1,0)$ ,  $\Lambda(1,1)$ , V(0,0), V(0,1), V(1,0), V(1,1)

Рисунок 1.3 – Модели неисправностей, описывающие функциональное проявление дефектов в процессе работы памяти.

#### 1.3.1 Неразрушающее тестирование памяти

Основным требованием, предъявляемым к неразрушающим тестам, является необходимость восстановления исходного состояния объекта тестирования

после выполнения процедуры тестирования. Поэтому все тестовые воздействия, направленные на активизацию неисправостей и проявление их в виде ошибок на выходах схемы, должны носить обратимый характер.

Простейшим способом реализации этого требования для случая неразрушающего тестирования памяти является сохранение всего ее содержимого в резервном буфере с последующим выпол-нением одного из классических разрушающих алгоритмов. Хотя этот способ позволяет использовать существующую ВАСТ, он потребует дублирования массива запоминающих элементов, а также дополнительного времени для сохранения и последующего восстановления содержимого памяти. Поэтому для большинства приложений он непригоден.

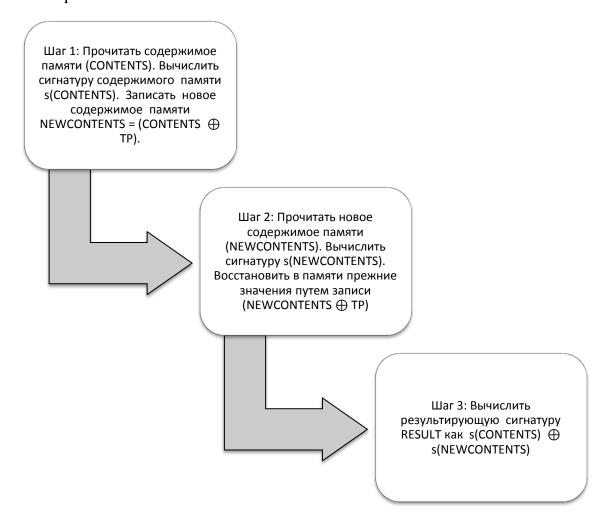

Другой подход был предложен в докладе Б.Конемана на семинаре Design For Testability в 1986 г. Обозначим через s(A) сигнатуру упорядоченного потока данных A длинной N, а через TP — поток тестовых данных той же длины. Тогда алгоритм работы метода можно сформулировать следующим образом (рисунок 1.4).

Для работы этого метода необходимо, чтобы используемые сигнатурные анализаторы обладали свойством линейности, потому что только в этом случае для исправной памяти будет получено детерминированное значение RESULT = s(TP). Несмотря на то что описанный алгоритм удовлетворяет требованиям неразрушающего тестирования и достаточно просто реализуется в программном или аппаратном виде, он обладает некоторыми существенными недостатками.

- а) некоторые неисправности генерируют на Шаге 1 и Шаге 2 одинаковые векторы ошибок. Такие неисправности не будут обнаружены за счет наложения ошибок друг на друга.

- б) предлагаемые тестовые последовательности состоят из двух элементарных циклов, содержащих по одной операции чтения и записи для каждой ячейки. Им соответствует простейший маршевый алгоритм ↑ r0(,w1;↑)(r1,w0). Не существует универсальных способов построения неразрушающих аналогов произвольных маршевых алгоритмов.

в) предложенный алгоритм не гарантирует обнаружение целого ряда неисправностей памяти.

Рисунок 1.4 – Последовательность неразрушающего тестирования памяти по методу Конемана.

#### 1.3.2 Тестирование по методу Николаидиса

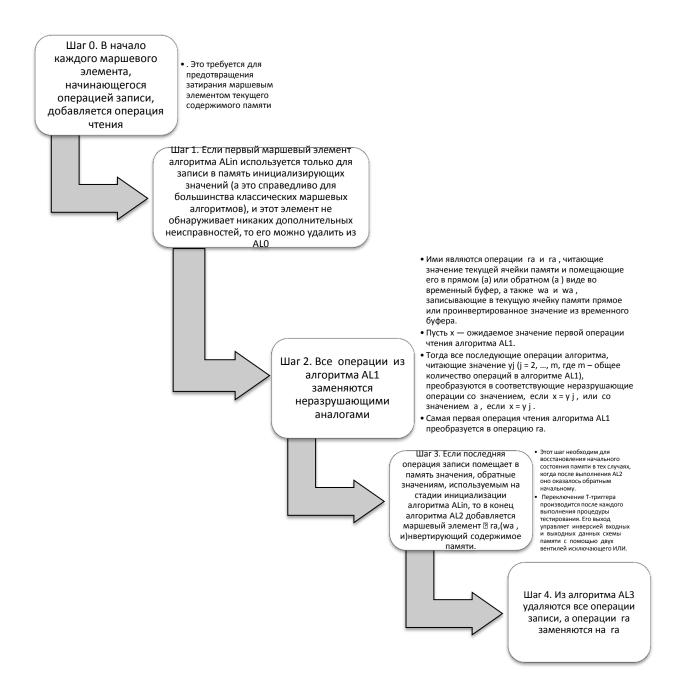

Из-за описанных недостатков метод Конемана не нашел широкого применения на практике. Вместо него в большинстве случаев используются методы, основанные на преобразовании классических маршевых тестов к неразрушающему виду. Последовательность шагов, требуемых для такого преобразования, была предложена М.Николаидисом. На вход преобразования поступает классический маршевый алгоритм ALin, промежуточные алгоритмы, получаемые на каждом шаге і, обозначаются через ALi. Последовательность тестирования по методу Николаидиса представлена на рисунке 1.5.

Рисунок 1.5 - Последовательность тестирования по методу Николаидиса.

Полученный на последнем шаге алгоритм AL3 представляет собой неразрушающую версию исходного маршевого алгоритма ALin. Он называется базовым неразрушающим тестом. Активизирующая неисправности модификация памяти в процессе его выполнения осуществляется путем инвертирования всего содержимого памяти.

Для обнаружения ошибок результаты всех операций чтения сжимаются с помощью сигнатурного анализатора в рабочую сигнатуру.

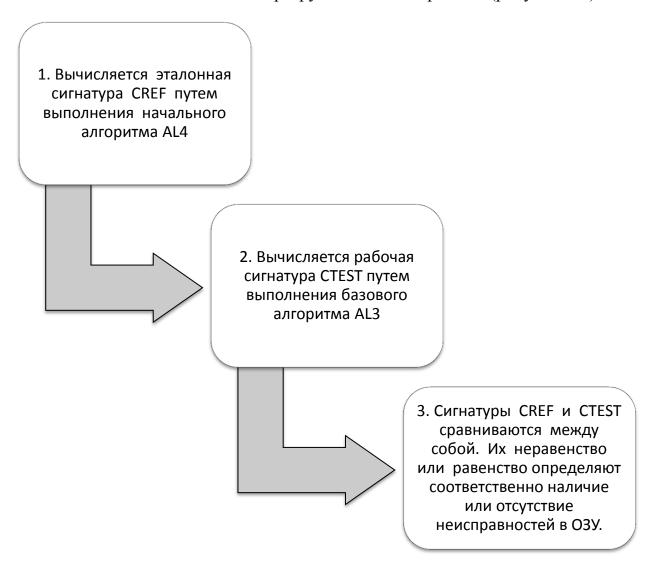

Для получения эталонной сигнатуры, соответствующей содержимому памяти без ошибок, перед выполнением базового алгоритма запускается начальный алгоритм, получаемый на шаге 4.

Опишем полную процедуру тестирования памяти алгоритмом с использованием базового и начального неразрушающих алгоритмов (рисунок 1.6).

Рисунок 1.6 - Полная процедура тестирования памяти алгоритмом с использованием базового и начального неразрушающих алгоритмов.

Описанной технологии неразрушающего тестирования также присущ ряд недостатков.

- а) существенно увеличивается сложность теста за счет добавления начального алгоритма, используемого для вычисления эталонной сигнатуры.

- б) не гарантируется 100-ная покрывающая способность даже для однократных неисправностей из-за эффекта маскирования.

#### 1.4 Требования к разрабатываемому модулю

Модуль подключается к микропроцессорной системе через интерфейс RS-232 для тестирования программной части, либо осуществления контроля. Основой устройства служит микроконтроллер семейства MSC-51. Микроконтроллер должен:

- а) обрабатывать полученные данные на основании имеющихся в программе;

- б) выводить информацию на дисплей.

Входными данными являются цифровые сигналы, выходящие из тестируемой микропроцессорной системы.

Выходными данными являются цифровые сигналы, генерируемые системой.

#### 2 Проектирование микропроцессорного модуля тестирования

# 2.1 Проектирование архитектуры модуля тестирования компонентов микропроцессорной системы

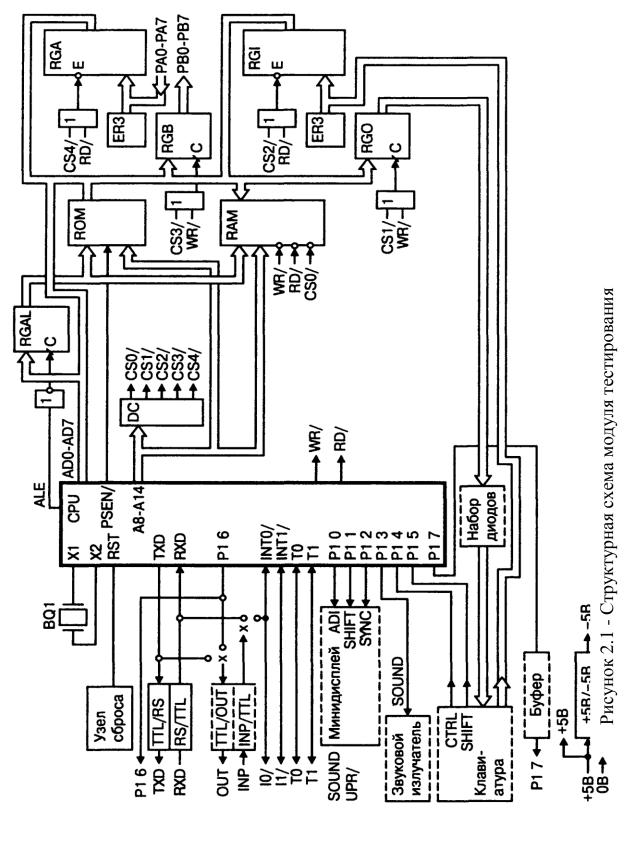

Структурная схема модуля тестирования компонентов микропроцессорной системы представлена на рисунке 2.1.

Система системы включает в себя:

- а) микропроцессор. Основные задачи: вычисление адресов команд и операндов, выборку и дешифрацию команд из основной памяти, прием и обработку запросов и команд, обработку данных и их запись в ОП, выработку управляющих сигналов для всех узлов и блоков ПК, переход к следующей команде;

- б) оперативная память. Основной задачей оперативной памяти является временное хранение данных;

- в) постоянная запоминающая память. Задачей постоянной памяти является хранение программ тестирования;

- г) узел сброса. Перезагрузка устройства;

- д) минидисплей. Отображение информации работы системы;

- е) клавиатура. Управление рабочим процессом;

- ж) TLL/RS, RS/TLL интерфейс RS-232;

- з) TLL/OUT, INP/TLL программно образуемый интерфейс «токовая петля»;

- и) регистры RGO/RGI служат для связи с клавиатурой;

- к) регистры RGA/RGB предназначены для организации 8-разрядных параллельных портов связи с внешними устройствами;

- л) ER1/ER2 резисторные матрицы служащие для подтягивания уровней высокого логического сигнала к потенциалу источника питания.

компонентов микропроцессорной системы

#### 2.2 Выбор аппаратного и программного обеспечения

# 2.2.1 Выбор компонентов модуля тестирования компонентов микропроцессорной системы

#### Обоснование выбора микроконтроллера

При выборе микроконтроллера руководствуемся тем, что для системы необходим наиболее простой контроллер на базе распространенной платформы. Выбираем микроконтроллер AT89C51 на платформе MCS-51 с 4Кбайт Flash памятью с поддержкой внутрисистемного программирования.

Микроконтроллеры семейства AT89 фирмы Atmel представляют собой 8ми разрядный CMOS микроконтроллер с низким энергопотреблением

Отличительные особенности микроконтроллера АТ89С51:

- а) высокая производительность и RISC архитектура с низким энергопотреблением;

- б) более 100 мощных инструкций большинство из них выполняются за один такт;

- в) 4 Кбайт Flash- памяти с поддержкой внутрисистемного программирования (ресурс: 1000 циклов записи/стирания);

- г) 128 байта PEROM;

- д) ресурс: 100000 циклов запись/ стирание;

- е) 32 программируемых линий І/О;

- ж) напряжение питания 5±20% В;

- з) полностью статический режим работы: от 0 до 24 МГц;

- и) два16-и разрядных таймера/счетчика с отдельным предварительным делителем частоты;

- к) программируемый полнодуплексный UART;

- л) шесть источников сигналов прерывания;

- м) пассивный (idle) и стоповый (power down) режимы;

- н) трехуровневая блокировка памяти программ;

- о) 38 выводов.

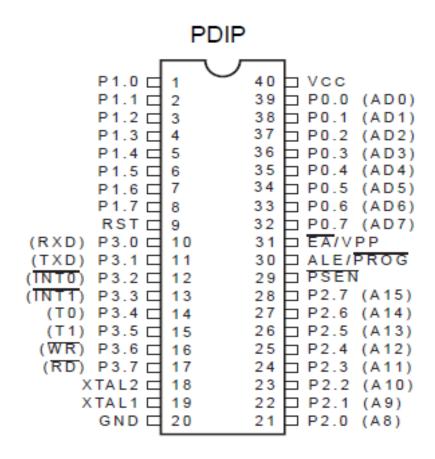

Назначение выводов микроконтроллера АТ89С51 представлено на рисун-

ке 2.2. Назначение портов микроконтроллера AT89C51 представлено на рисунке 2.3.

| VCC                    | • Вывод источника питания                                                                                                                                                                                                                                                                                                                                                             |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GND                    | • Земля                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| RST                    | •Вход сброса (Reset) •Чтобы сбросить устройство, необходимо подать сигнал логической 1 на время двух машинных тактов. В это время генератор сбросит устройство                                                                                                                                                                                                                        |  |  |

| ALE/PROG               | <ul> <li>Address Latch Enable - разрешение блокировки адреса</li> <li>Защелкивает импульсом младший байт адреса на время доступа ко внешней памяти</li> <li>Также является входом импульса во время программирования Flash. Нормальный ALE сигнал должен быть выдан при постоянном показателе - 1/6 частоты генератора, и может быть использован для внешней синхронизации</li> </ul> |  |  |

| Program Store ENable   | •Строб чтения для внешней памяти программ •Когда АТ89С51 выполняет программный код из внешней памяти, активизируется каждый второй машинный цикл, за исключением тех случаев, когда два сигнала проскакивают во время доступа к внешней памяти данных                                                                                                                                 |  |  |

| External Access Enable | <ul> <li>• Разрешение внешнего доступа</li> <li>• Чтобы выбирать код из внешних программных позиций памяти, находящихся в диапазоне от 0000Н до FFFFH, необходимо закоротить этот контакт на общий провод (GND)</li> </ul>                                                                                                                                                            |  |  |

| XTAL1                  | • Инвертированный вход усилителя генератора и вход на внутренние часы                                                                                                                                                                                                                                                                                                                 |  |  |

| XTAL2                  | •Инвертированный выход усилителя генератора                                                                                                                                                                                                                                                                                                                                           |  |  |

Рисунок 2.2 - Назначение выводов микроконтроллера АТ89С51

## Порт 0

- •8-битный открытый двунаправленный порт Вв./Выв. На каждый выход этого порта можно нагрузить восемь входов TTL. При записи логической 1 в порт 0, контакты порта могут быть использованы как высокоимпедансные входы

- Может быть сконфигурирован как мультиплексируемый младший адрес, либо как шина данных, во время обращений ко внешней программе или памяти данных. В этом режиме Порт 0 использует внутреннее напряжение

- •Во время программирования Flash на Порт 0 поступают байты кода. Он же их и выводит во время веритификации программы. Напряжение программирования UPP требуется и при веритификации данных

# Порт 1

- •Двунаправленный порт ввода/вывода на 8 битов со внутренним напряжением питания

- •Выходной буфер Порта 1 может быть нагружен на четыре входа/выхода ТТL. При записи логической 1 в порт 1, контакты порта могут быть использованы как входы. Так как Порт 1 использует внутреннее напряжение питания, уровень потребляемого тока (IIL) извне будет минимален

- •При программировании Flash на Порт 1 поступают младшие биты адреса. Тоже самое происходит и во время веритификации

## Порт 2

- Двунаправленный порт ввода/вывода на 8 битов со внутренним напряжением питания

- Выходной буфер Порта 2 может быть нагружен на четыре входа/выхода TTL. При записи лог.1 в порт 2, контакты порта могут быть использованы как входы. Так как Порт 2 использует внутреннее напряжение питания, уровень потребляемого тока (IIL) извне будет минимален

- Принимает старшие биты адреса и некоторые управляют сигналам во время программирования Flash и во время проверки

- Порт 2 выдает старший байт адреса во время выборки из внешней памяти программ и во время доступов ко внешней памяти данных, которые используют 16-битные адреса (MOVX DPTR). В этом случае, при лог.1, более высокое потребление тока от внутреннего источника. В время доступов ко внешней памяти данных, которые используют 8-битные адреса (MOVX @ RI), Порт 2 выдает содержимое Специального Функционального Регистра P2

## Порт 3

- 8-битный двунаправленный порт Вв./Выв

- Выходы Порта 3 могут быть нагружены на четыре входа TTL.

При записи логической 1 в порт 3, контакты порта могут быть использованы как входы

- Обеспечивает выполнение различных специализированных функций AT89C51

Специализированное назначение выводов порта 3 представлено на рисунке 2.4.

| P3.0 | • RXD (Принимаемые данные последовательного порта)  |

|------|-----------------------------------------------------|

| P3.1 | • TXD (Передаваемые данные последовательного порта) |

| P3.2 | • INTO (Внешнее прерывание 0)                       |

| P3.3 | • INT1 (Внешнее прерывание 1)                       |

| P3.4 | • Т0 (внешний вход таймера 0)                       |

| P3.5 | • Т1 (внешний вход таймера 1)                       |

| P3.6 | • WR(Внешний строб записи)                          |

| P3.7 | • WD(Внешний строб чтения)                          |

Рисунок 2.4 - Специализированное назначение выводов порта 3 микроконтроллера AT89C51.

Предельные допустимые параметры микроконтроллера АТ89С51:

- а) рабочая температура ..... -55°C to +125°C;

- б) температура хранения ..... -65°С to +150°С;

- в) напряжение на любом контакте, что соединён с GND ...... -1.0 V to  $+7.0~\mathrm{V};$

- г) максимальное рабочее напряжение ...... 6.6 V;

- д) постоянный ток на выходе ...... 15.0 mA.

На рисунке 2.5 представлена схема расположения выводом микроконтроллера AT89C53.

Рисунок 2.5 – Описание выводов микроконтроллера АТ89С51.

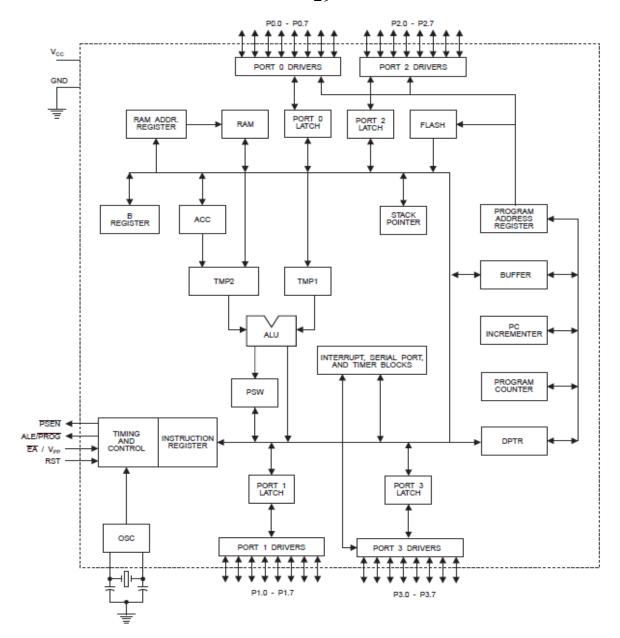

Логическая структура микроконтроллера AT89C51 представлена на рисунке 2.6.

### Обоснование выбора запоминающих устройств

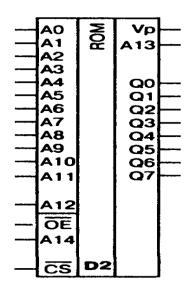

Основой выбора запоминающих устройств были выдвинуты основные параметры как относительно недорогая стоимость и достаточный объем для внесения сложных программ тестирования. На основании этого была выбрана микросхема постоянно запоминающего устройства М2716.

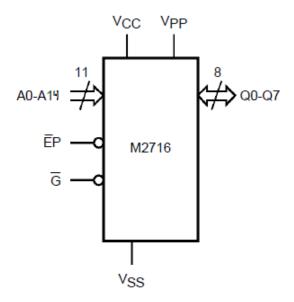

Интегральное исполнение постоянного запоминающего устройства M2716 представлено на рисунке 2.7.

Рисунок 2.6 – Логическая архитектура микроконтроллера АТ89С51.

Назначение выводов М2716:

- а) А0-А14 выводы адресации;

- б) Q0-Q7 выходы данных;

- в) CS сигнал доступа к микросхеме;

- г) ОЕ вход сигнала чтения;

- д) Vp напряжение питания.

На рисунке 2.8 представлена логическая схема ПЗУ М2716.

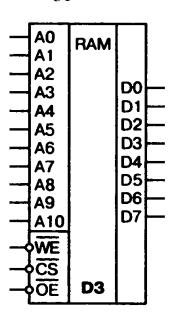

В качестве оперативного запоминающего устройства выбрана микросхема НМ-6516.

Интегральное исполнение оперативно запоминающего устройства НМ-

6516 представлено на рисунке 2.9.

Рисунок 2.7 - Интегральное исполнение ПЗУ М2716.

Рисунок 2.8 – Логическая схема ПЗУ М2716.

Назначение выводов НМ-6516:

- а) А0-А10 выводы адресации;

- б) D0-D7 входы/выходы данных;

- в) CS сигнал доступа к микросхеме;

- г) ОЕ вход сигнала чтения;

- д) WE вход управляет записью в порт ввода/вывода.

Рисунок 2.9 - Интегральное исполнение ОЗУ НМ-6516.

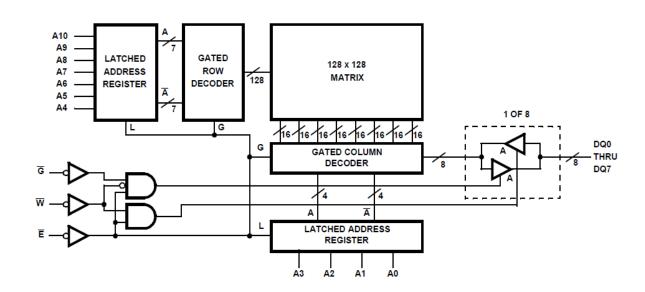

На рисунке 2.10 представлена функциональная схема оперативно запоминающего устройства.

Рисунок 2.10 – Функциональная схема ОЗУ НМ-6516.

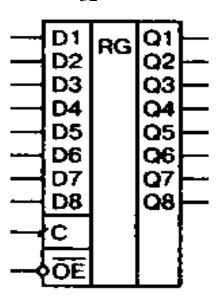

#### Обоснование выбора регистров-защелок

Выбор регистров-защелок производится по следующим параметрам: напряжение питания  $\pm$  5B, 8-ми битные порты ввода/вывода.

Защелки sn74ls373(D6,D11), sn74ls374(D4,D5,D10), sn74ls138(D7), sn74ls04(D8.1-D8.6), sn74ls32(D9.1-D9.4).

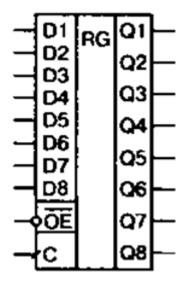

Интегральное исполнение sn74ls373 представлено на рисунке 2.11.

Рисунок 2.11 - Интегральное исполнение регистра sn74ls373. Интегральное исполнение sn74ls374 представлено на рисунке 2.12.

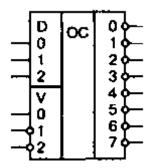

Рисунок 2.12 - Интегральное исполнение регистра sn74ls374. Интегральное исполнение sn74ls138 представлено на рисунке 2.13.

Рисунок 2.13 - Интегральное исполнение sn74ls138. Интегральное исполнение sn74ls04 представлено на рисунке 2.14.

Рисунок 2.14 - Интегральное исполнение sn74ls04.

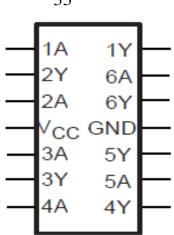

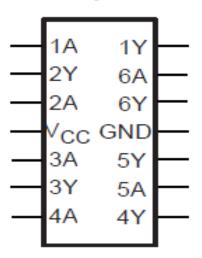

Назначение выводов sn74ls373, sn74ls374, sn74ls138, sn74ls04, sn74ls32:

- а) D1-D8 входы данных;

- б) Q1-18 выходы данных;

- в) ОЕ вход сигнала чтения;

- г) С тактовый сигнал.

Интегральное исполнение sn74ls32 представлено на рисунке 2.15.

Рисунок 2.15 - Интегральное исполнение sn74ls32.

## Обоснование выбора жидкокристаллического индикатора

В качестве жидкокристаллического индикатора была выбрана микросхема MT-08S2A-2FLA.

Общее описание:

а) реальная работоспособность при низких и высоких температурах в отличие от импортных аналогов. Все наши индикаторы имеют исполнения с рабочим диапазоном температур от -30 до + 70 градусов Цельсия;

- б) белорусский/украинский/казахский знакогенераторы кроме стандартных русско/английских символов. Также удобной особенностью является использование в наших ЖК индикаторах знакогенератора 5 х 8 точек, в следствие чего все буквы кириллицы выглядят понятнее и больше;

- в) дополнительная страница знакогенератора в кодировке Win-CP1251 (для буквенно-цифровых ЖК индикаторов) позволяет упростить программирование индикаторов при написании программ в среде Microsoft Windows;

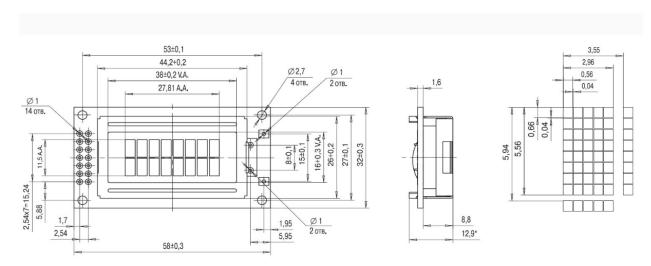

Технические характеристики:

- а) контроллер: КБ1013ВГ6;

- б) подсветка: Янтарная;

- в) тип стекла: FSTN Positive;

- г) разрешение.: 08x2;

- д) размер индикатора, мм: 58х32х12.9;

- е) видимая область, мм: 38х16;

- ж) символ, мм: 3.55х5,56;

- з) температура рабочая: -20+70 С;

- и) температура хранения: -30+80.

На рисунке 2.16 представлен чертеж жидкокристаллического индикатора MT-08S2A-2FLA.

Рисунок 2.16 – Чертеж ЖКИ MT-08S2A-2FLA.

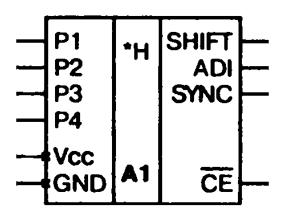

Интегральное исполнение жидкокристаллического индикатора представлено на рисунке 2.17.

Рисунок 2.17 - Интегральное исполнение жидкокристаллического индикатора MT-08S2A-2FLA.

Назначение выводов жидкокристаллического индикатора:

- а) Р1-Р4 входные данные;

- б) GDN общий провод;

- в) Усс напряжение питания;

- г) SHIFT сигнал состояния регистра;

- д) ADI;

- e) SYNC;

- ж) CE.

#### 2.2.2 Выбор программного обеспечения

В качестве языка программирования был выбран Assembler.

Само слово ассемблер (assembler) переводится с английского как «сборщик». На самом деле это название программы-транслятора, принимающей на входе текст, который содержит условные обозначения машинных команд, удобные человеку, и переводящей их в последовательность соответствующих кодов машинных команд, которые понятны процессору. Условные обозначения команд (в отличие от машинных), запомнить довольно несложно, так как они являются сокращениями от английских слов. Язык условных обозначений и называют языком ассемблера.

Ассемблер — это машинно ориентированный язык программирования, который позволяет работать с микропроцессорной системой непосредственно, напрямую. Команды ассемблера полностью идентичны командам процессора,

но различные модели процессоров обладают своим собственным набором команд, поэтому, существуют и разновидности, или диалекты, языка ассемблера. Так как ассемблер зависит от устройства процессора, а тип процессора строго определяет набор доступных команд машинного языка, то программы на ассемблере не переносимы на другую компьютерную архитектуру.

Общепринятого стандарта для синтаксиса языков ассемблера не существует. Большинство разработчиков языков ассемблера придерживаются общих традиционных подходов. Основные такие стандарты — Intel-синтаксис и AT&T-синтаксис.

Общий формат записи инструкций одинаков для обоих стандартов:

[метка:] опкод [операнды] [;комментарий]

Опкод — это и есть сама ассемблерная команда, мнемоника инструкции для процессора. К ней можно добавить префиксы (например, повторения, изменения типа адресации). В качестве операндов могут выступать константы, названия регистров, адреса в оперативной памяти и так далее. Различия между стандартами Intel и AT&T заключаются в порядке перечисления операндов и их синтаксиса при разных методах адресации.

Для всех процессоров одной архитектуры или семейства архитектур используются как правило одинаковые команды. Эти команды приведены в спецификации процессоров.

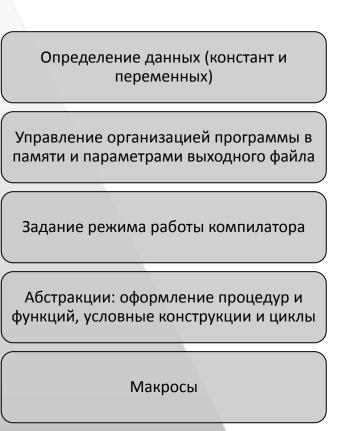

Помимо ассемблерных команд, программа может включать в себя различные директивы — команды, которые не переводятся непосредственно в машинные инструкции и управляют работой компилятора. Набор и синтаксис их значительно отличается и зависит не от аппаратной платформы, а от используемого компилятора. Примеры директив представлены на рисунке 2.18.

Несмотря на то, что Ассемблер не всегда использует внутренние инструкции самих машин, это практически не вызывает потери в быстродействии, наоборот лишь предоставляя пользователю возможности для использования макрокоманд.

Рисунок 2.18 – Примеры директив языка Ассемблер.

Обладая достаточно ограниченным набором команд и действий, язык ассемблера является универсальным средством, если вы хотите создать максимально быстро исполняемый код, а также пошагово отследить процессы, выполняемые машиной.

Исходя из этого выделим очевидные достоинства:

- а) быстродействие. Быстрее только использовать непосредственные инструкции процессора;

- б) безопасность. Низкоуровневость в данном случае практически исключает наличие белых пятен в коде;

- в) эффективность использования возможностей конкретной платформы. Ориентированность на используемую машину позволяет иметь серьезное преимущество по сравнению с высокоуровневыми языками;

г) понимание исполняемого кода программистом. На таком уровне программирования код и действие имеют очевидно причинно-следственную связь.

Однако, Ассемблер обладает и рядом недостатков:

- а) трудно выучить. Специализация на платформу, несколько диалектов все это не способствует быстрому изучению и пониманию;

- б) тяжело читать. Большой листинг, простые однотипные операции;

- в) написание программ. Некоторые примитивные операции, описываемые в языках высокого уровня одной строкой, здесь могут вызывать настоящую головную боль у программиста;

- г) большинство используемых машин просто не нуждается в таком примитивном языке, как ассемблер;

- д) высокий порог входа. Представить исполняемый код в языке ассемблера сможет почти любой программист средней руки. Сделать это эффективнее компилятора лишь малая часть;

- е) сильно ограниченное количество библиотек, сообществ, вспомогательных ресурсов по современным меркам.

# 2.2.3 Технические характеристики каналов связи между проектируемым устройством и тестируемым устройством

Разрабатываемое устройство подключается к тестируемому устройству по средствам интерфейсов RS-232 и «токовая петля»

RS-232 (Recommended Standard 232) - стандарт последовательной асинхронной передачи двоичных данных между терминалом и коммуникационным устройством.

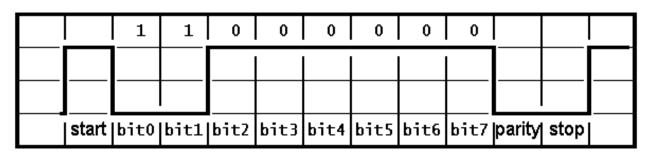

Основные особенности интерфейса RS-232 представлены на рисунке 2.19.

Обычно, DTE (ООД) является компьютером, а DCE (ОПД) - это периферийные устройства (мышь, принтер, модем).

На рисунке 2.20 показана распайка вилки оборудования обработки данных (DTE). Розетка устройства передачи данных (DCE) распаяна так, что два разъема стыкуются напрямую, или через кабель, распаянный «контакт в контакт».

Можно передавать информацию между двумя устройствами на расстояние до 15 метров

Информация передается по проводам цифровым сигналом с двумя уровнями напряжения

Логическому "0" соответствует положительное напряжение (от +5 до +15 В для передатчика), а логической "1" отрицательное (от -5 до -15 В для передатчика)

Асинхронная передача данных осуществляется с фиксированной скоростью при самосинхронизации фронтом стартового бита

Обеспечивает соединение двух устройств, одно из которых называется DTE (Data Terminal Equipment) - ООД (Оконечное Оборудование Данных), второе — DCE (Data Communications Equipment) - ОПД (Оборудование Передачи Данных)

Все сигналы в интерфейсе потенциальные, с номинальными уровнями +15В и -15В относительно общего провода (Signal Ground)

Поток данных передается по одному проводу бит за битом

В отсутствие передачи данных линия находится в состоянии логической единицы (-15B).

Рисунок 2.19 - Основные особенности интерфейса RS-232.

Для правильного соединения приемопередатчики на устройствах, совершающих обмен информацией, нужно запрограммировать одинаково. Т.е. с одинаковой скоростью, количеством битов данных (7 или 8), типом контроля по четности и длиной стопового бита. При точных расчётах времени на передачу массива байтов наравне с битами данных надлежит учесть все служебные биты. На рисунке 2.21 представлена схема передачи фрейма в последовательном интерфейсе RS 232.

Рисунок 2.20 - Распайка вилки оборудования обработки данных (DTE).

Токовая петля является способом передачи информации посредством измеряемых значений силы электрического тока. Чтобы задать измеряемые значения тока - используют управляемый источник тока. Различают аналоговую токовую петлю и цифровую токовую петлю по типу передаваемой информации.

Рисунок 2.21 – Схема передачи фрейма в последовательном интерфейсе

#### RS 232.

Цифровая токовая петля используется в телекоммуникационном оборудовании и компьютерах для последовательной передачи данных.

Основные особенности работы цифровой токовой петли приведены на рисунке 2.22.

Аналоговая токовая петля применяется при передаче аналогового сигнала по паре проводов для лабораторного оборудования, система управления производством и т. д. Основные особенности работы аналоговой токовой петли приведены на рисунке 2.23.

Принципиальная электрическая схема тестирующего устройства представлена в приложении А.

### 2.3 Алгоритм работы микропроцессорной системы

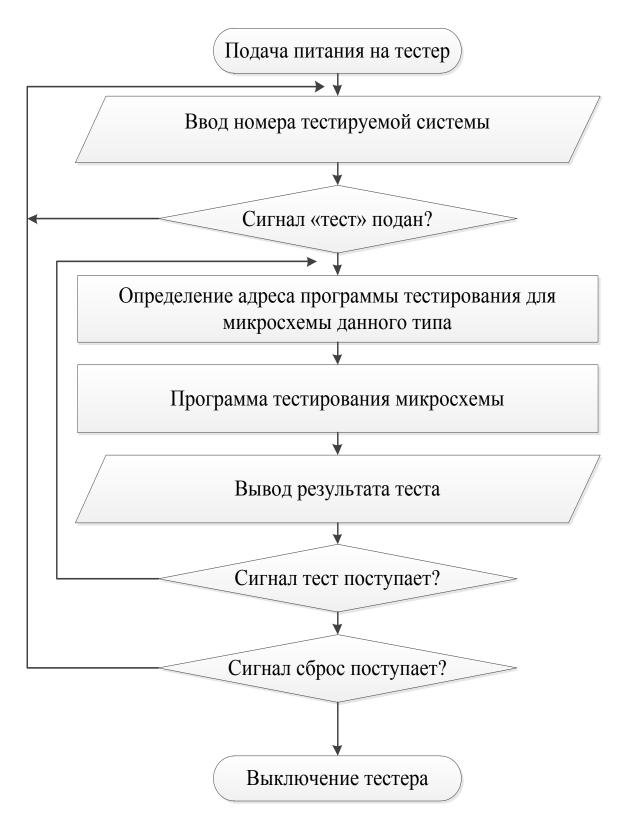

На подключенный к микропроцессорному модулю тестер подается питание. Следом следует ввести номер тестируемой системы. После выявления номера тестируемой системы проводится проверка подачи сигнала тестирования, если сигнала нет, то алгоритм заново переходит на стадию установки номера тестируемой системы. Если сигнал «тест» подан, то система определяет адрес подпрограммы тестирования для микросхемы. Следом проводится тестирование микросхемы, с последующим выводом результата на экран. Если сигнал тест к тому моменту все еще поступает, то программа возвращается на стадию определения адреса подпрограммы тестирования. Если сигнал не поступает проводится проверка сигнала сброса. Если сигнал есть, то программа переходит на стадию выбора номера тестируемой системы. В противном случае идет выключение тестера.

Алгоритм работы модуля тестирования компонентов микропроцессорной системы представлен на рисунке 2.24.

# 2.4 Методы обеспечения качества модуля тестирования компонентов микропроцессорной системы

На рисунке 2.25 представлен ориентированный метод расчета надежности модуля.

Стандарт цифровой токовой петли использует отсутствие тока как значение SPACE (низкий уровень, логический ноль) и наличие сигнала — как значение МARK (высокий уровень, логическая единица)

Отсутствие сигнала в течение длительного времени интерпретируется как состояние BREAK (обрыв линии)

Данные передаются стартстопным методом, формат посылки совпадает с RS-232 Может использоваться на значительных расстояниях (до нескольких километров)

Для защиты оборудования применяется гальваническая развязка на оптоэлектронных приборах

Из-за неидеальности источника тока, максимально допустимая длина линии (и максимальное сопротивление линии) зависит от напряжения, от которого питается источник тока

Источник тока может располагаться в приемном или передающем конце токовой петли

Применяется смещенный диапазон 4-20 мА

Нулевое значение тока в цепи означает обрыв линии и позволяет легко диагностировать такую ситуацию

Интерфейс позволяет использовать разнообразные датчики (давления, потока, кислотности и т. д.) с единым электрическим интерфейсом

Может использоваться для управления регистрирующими и исполнительными устройствами: самописцами, заслонками

Точность не зависит от длины и сопротивления линии передачи, поскольку управляемый источник тока будет автоматически поддерживать требуемый ток в линии

Несколько приемников можно соединять последовательно, источник тока будет поддерживать требуемый ток во всех одновременно

Рисунок 2.23 - Основные особенности работы аналоговой токовой петли. В данном методе расчета применяются следующие показатели качества. Вероятность безотказной работы:

$$P(t) = e^{-\lambda_{\Sigma}t} = e^{-\sum_{i=1}^{K} N_i \lambda_{0i} \cdot t} = 0,979953654 = 97\%;$$

(2.1)

наработка на отказ

$$T_0 = \frac{1}{\lambda_{\rm r}} = 49000 \,\mathrm{y}. \tag{2.2}$$

Рисунок 2.24 - Алгоритм работы модуля тестирования компонентов микропроцессорной системы.

| Наименование               |                       |                               |

|----------------------------|-----------------------|-------------------------------|

| Количество                 | Интенсивность отказов | Интенсивность отказов наборов |

|                            |                       |                               |

| Микросхемы                 |                       |                               |

| 13                         | 0,01                  | 0,13                          |

|                            |                       |                               |

| Резисторы                  |                       |                               |

| 13                         | 0,5                   | 6,5                           |

|                            |                       |                               |

| Резисторные матрицы        |                       |                               |

| 2                          | 0,8                   | 1,6                           |

|                            |                       |                               |

| Конденсаторы               |                       |                               |

| 17                         | 0,4                   | 6,8                           |

|                            |                       |                               |

| Преобразователь, резонатор |                       |                               |

| 2                          | 1,4                   | 2,8                           |

|                            |                       |                               |

| Диоды                      |                       |                               |

| 11                         | 0,02                  | 0,22                          |

|                            |                       |                               |

| Транзисторы                |                       |                               |

| 3                          | 0,5                   | 1,5                           |

|                            |                       |                               |

|                            | Разьемы               |                               |

| 4                          | 0,05                  | 0,2                           |

Рисунок 2.25 - Ориентированный метод расчета надежности модуля.

- 3 Реализация микропроцессорного модуля тестирования

- 3.1 Конструкторско-технологическая документация системы

### 3.1.1 Описание процесса изготовления печатной платы

Чтобы отвечать новым требованиям рынка, изготовители печатных плат (ПП) форсируют поиск новых и прогрессивных технологических процессов на каждом этапе производства.

Металлизация сквозных отверстий и меднение поверхности подвергаются серьезному исследованию, так как они составляют основу процессов, которые формируют проводящие дорожки и соединения через сквозные отверстия.

### Палладиевая система металлизации

Вследствие недостатков существующих процессов, таких как химическое меднение или металлизация с использованием углерода, внедряется новая система металлизации, основанная на адсорбции палладия. Она предназначена для изготовления гибких и жёсткоогибких плат, где при наслаивании всегда используются адгезивные слои. Эти прослойки чувствительны к воздействию высокой щелочности, присутствующей при химическом осаждении меди. Новая технология обеспечивает сильно укороченное время процесса, что минимизирует воздействие щелочи. Кроме того, она создает условия, которые обеспечивают сцепление палладия только с полиимидным диэлектриком, а не с медью. Благодаря этому не требуется травление медной поверхности перед электролитическим осаждением, как это имеет место при углеродной системе. А микротравление медной поверхности увеличивает пористость, что снижает надёжность межсоединений внутренних слоёв.

### Электроосаждение меди

Проблему электроосаждения меди составляет получение равномерной толщины и однородной поверхности без потери её механических свойств (сопротивление растяжению и относительное удлинение).

Значимость этих свойств особенно возрастает при высоком термическом напряжении в случае бессвинцовой пайки.

Проблема равномерной толщины чаще всего встречается в двух основных

местах: на поверхности и в сквозных металлизированных отверстиях. В первом случае есть опасность избыточной металлизации изолированных дорожек, а во втором — сложно выполнить требование минимальной толщины меди в центре отверстия с высоким аспектовым отношением. Поверхностная однородность иногда нарушается гранулами самого разного происхождения, что несовместимо с применением золотой проволоки для соединений.

Эти проблемы помогут решить новые разработки:

- а) новые химические добавки, улучшающие распределение;

- б) многочисленные усовершенствования существующих добавок;

- в) устранение гранул благодаря использованию нерастворимого анода;

- г) заполнение отверстий.

Электроосаждение с высокой рассеивающей способностью электролита

В последние годы появилось новое поколение систем меднения с высокой рассеивающей способностью электролита. Эти ванны спроектированы для современных значений плотности гальванических токов, которые ниже традиционных 2,7–3,2 А/дм2, применявшихся в прошлом для производства двухсторонних и более простых плат. Они обеспечивают требуемые физические свойства при плотности постоянного тока от 0,5 до 2 А/дм2, создавая блестящее пластичное покрытие. В них применяется особая смесь органических добавок, включающих уникальное выравнивающее средство. Выравниватель играет ключевую роль в повышении рассеивающей способности, особенно при сочетании с перемешиванием. Некоторые из этих ванн могут обеспечить рассеивающую способность выше 80% для отверстий с аспектовым отношением 10:1 за 90 мин при плотности тока 1,6 А/дм2.

### Металлизация отверстий с заполнением

Для выполнения требований межсоединений высокой плотности (HDI) наилучшим вариантом соединения различных слоёв в технологии их наращивания быстро становится металлизация отверстий с заполнением. Она обеспечивает долговременную надёжность и печатных плат, и корпусов чипов.

Металлизация переходных отверстий с заполнением в ваннах с импульс-

ным или постоянным током, особенно с применением новых электролитов, имеет много преимуществ, поскольку не требует выпрямления тока и управления им. Кроме того, системы металлизации постоянным током стабильны и не нуждаются в постоянной регенерации электролитов.

Заполнение отверстий основано на интенсивном осаждении ионов высокой концентрации, связанных с выравнивателем низкой концентрации и блескообразующими добавками. Большинство таких систем нуждаются в оптимизированном потоке раствора, что дает возможность выравнивателю аккумулироваться на поверхности. Это сдерживает осаждение наверху, в то время как на дне отверстия осаждение продолжается.

Новое поколение электролитов для заполнения отверстий медью разработано для работы в режиме постоянного тока. Операция проходит в стандартных ваннах в течение 1 ч при плотности тока от 1,10 до 3,20 А/дм2.

### Финишные покрытия

Эволюция финишных покрытий опережает все химические процессы, поскольку сложность конструкций и ограничения, связанные с бессвинцовыми и безгалогенными процессами, заставляют промышленность пристальнее взглянуть на то, как нынешние финишные покрытия соответствуют этим требованиям. Финишные покрытия полностью предназначены для соединений, будь то паяное, проволочное или даже прижимное соединение. В зависимости от вида, образованного паяным контактом интерметаллического соединения (ИМС) финишные покрытия подразделяются на две категории: NiSn и CuSn.

В первую входят ENIG (химический никель и иммерсионное золото—IAu) и ENEPIG (химический никель, химический палладий и иммерсионное золото), а во вторую — OSP (органии ческие паяемые покрытия), иммерсионное серебро (IAg), иммерсионное олово (ISn) и DIG (прямое покрытие иммерсионным золотом). В отличие от CuSn, для NiSn требуется более высокая температура при сборке и, кроме того, эта группа содержит фосфористый слой.

#### **ENIG**

Это покрытие получается химическим осаждением фосфористого никеля

на катализированную медную поверхность с последующим нанесением на него тонкого слоя иммерсионного золота. ENIGG-покрытие марки IPCC4552 имеет никелевый слой толщиной 3–6 мкм и слой иммерсионного золота толщиной 0,05–0,1 мкм. Это – универсальное покрытие, хорошо паяется, имеет отличную электропроводность, к нему легко присоединять алюминиевую проволоку. Визуальный контроль его очень прост. Толщина покрытия легко определяется с помощью неразрушающего рентгенофлуоресцентного спектрального анализа. Срок годности покрытия при хранении составляет 12 месяцев.

### **ENEPIG**

Покрытие ENEPIG формируется из слоя химически осажденного никеля толщиной 3–6 мкм и нанесенного на него слоя химического палладия толщиной 0,1–0,2 мкм, покрываемого затем тончайшим слоем (0,02–0,05 мкм) иммерсионного золота. Оно появилось в середине 90-х годов и позднее среди специалистов получило название универсального покрытия благодаря многостороннему использованию: в процессах пайки, соединении с золотой и алюминиевой проволоками, в контактных соединениях. Однако оно не нашло широкого распространения, как ожидалось, особенно в области пайки эвтектикой, используемой сегодня. Дело в том, что несовместимость свинца с палладием мешала образованию однородного ИМС NiSn.

К 2006 году на ENEPIG снова обратили внимание, когда промышленность оценивала свои возможности в условиях бессвинцовой сборки. Для него пришел звёздный час, поскольку ENEPIG обеспечило одно из самых прочных паяных соединений с бессвинцовым сплавом SAC (SnAgCu). После выдерживания в течение 1 тыс. ч при температуре 150°C не было выявлено какиххлибо ухудшений в прочности паяного соединения. Исследование под растровым электронным микроскопом и элементный анализ показали, что наличие палладия в этом соединении значительно сокращает расширение ИМС. Всё это делает ENEPIG лидером при выборе финишного покрытия при необходимости пайки бессвинцовыми сплавами типа SAC.

#### **DIG**

Это относительно новое финишное покрытие, считающееся перспективным для бессвинцовой технологии. Создается осаждением золота толщиной 0,05 мкм непосредственно на медную поверхность. Процесс представляет собой сочетание погружения с химическим (автокаталитическим) осаждением, в результате чего значительно ограничивается диффузия меди к поверхности. Покрытие применимо, в частности, для ПП, предназначенных для работы в ВЧ-диапазоне, где ENIG и ENEPIG неприемлемы, так как в этом случае целостность проходящего сигнала может нарушаться из-за скинэффекта при наличии толстого никелевого слоя.

DIG образует CuSn интерметаллические соединения с припоями как из эвтектических, так и бессвинцовых сплавов SAC. Это покрытие выдерживает многократные термические нагрузки. Образующиеся паяные соединения не имеют граничных пор, при хранении до сборки оно не образует интерметаллические соединения и "усы". DIG допускает химическое мягкое золотое покрытие и при толщине 0,6 мкм обеспечивает идеальную поверхность для золотого проволочного монтажа. Этот процесс используется в основном в Японии, преимущественно при корпусировании, но его применение постоянно расширяется.

# Иммерсионное серебро

Хотя этот вид покрытия давно известен в промышленности, малая осведомлённость об обращении с ним и его хранении мешали продвижению иммерсионного серебра на рынок. Сейчас ведутся дополнительные исследования по его совместимости с бессвинцовыми припоями и новой технологии пайки. В последнее время поступали сообщения о наличии граничных пор, но это явление было хорошо изучено и установлены причины; небольшая модификация процесса позволяет предотвратить этот дефект.

# Иммерсионное олово

Это покрытие прошло многочисленные усовершенствования и хорошо закрепилось в производстве ПП. Благодаря смачиваемости и равномерности по толщине иммерсионное олово идеально при использовании упругих штырьков

и запрессованных контактов. При том, что иммерсионное олово представляет собой бессвинцовое финишное покрытие, связанные с новой технологией более высокие температуры требуют изменений в технических условиях процесса осаждения.

Покрытие иммерсионным оловом не занимает большое место в производстве ПП по двум причинам: образование интерметаллических соединений между оловом и низлежащей медью и подверженность образованию "усов". Исследования по определению наилучших технологических режимов в отношении обоих недостатков продолжаются, и уже найдены добавки, которые предотвратят образование "усов"

# 3.1.2 Проектирование печатной платы модуля тестирования в редакторе Dip Trace

DipTrace это современная система сквозного проектирования.

Основные функции DipTrace представлены на рисунке 3.1.

Компоненты - составляющие редактора DipTrace приведены на рисунке 3.2.

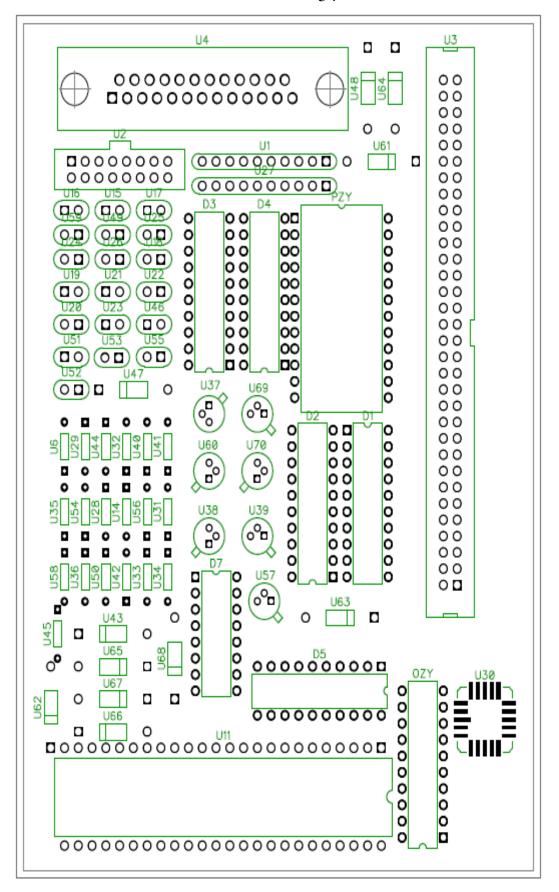

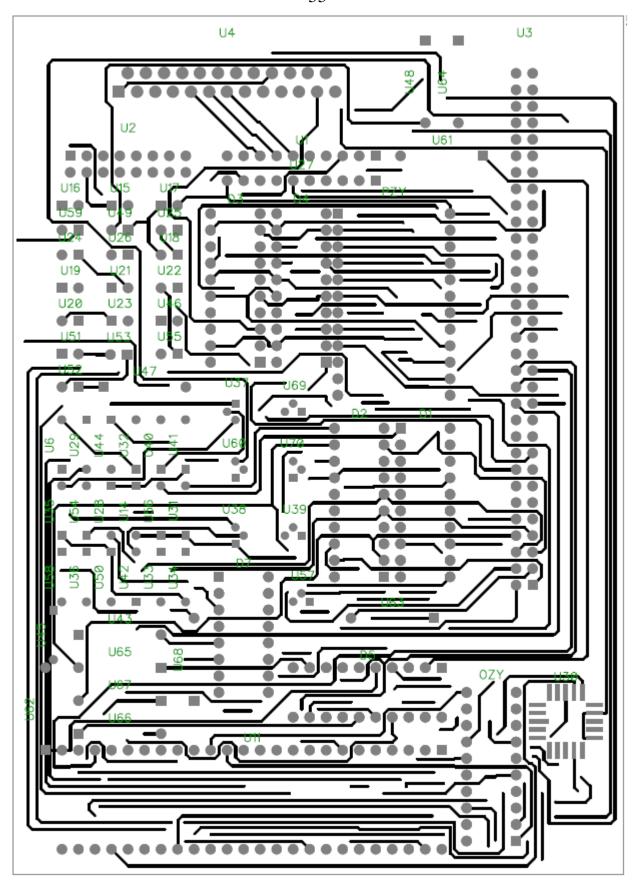

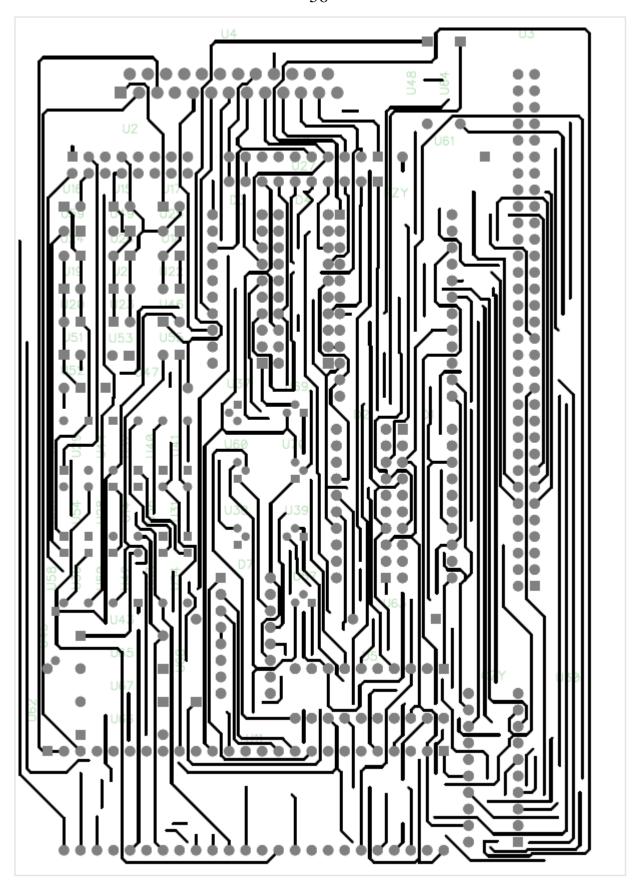

На рисунках 3.3, 3.4 и 3.5 представлена страссированная печатная плата модуля тестирования компонентов микропроцессорной системы.

# 3.2 Описание особенностей программирования модуля тестирования компонентов микропроцессорной системы

AVR Studio 5 - современное профессиональное интегрированное средство разработки, предназначенное для создания и отладки прикладных программ для AVR микропроцессоров в среде Windows. AVR Studio 5 включает ассемблер и симулятор.

Ключевым окном в AVR Studio является окно исходного текста программы. Если открыт объектный файл, то автоматически формируется окно исходного текста программ. В нем будет отображаться код, который исполняется в эмуляторе или программном симуляторе. Текстовый маркер постоянно будет находиться на той строке, которая будет исполнена в следующем цикле.

Интуитивно-понятный пользовательский интерфейс. Многоуровневая иерархия и поддержка многолистовых схем позволяет быстро и эффективно разрабатывать сложные принципиальные схемы. Преобразование схемы в плату, обновление проекта из измененной схемы и обратная аннотация производятся одним кликом. Все объекты подсвечиваются при работе. Учебник содержит пошаго вые рекомендации

Удобное ручное и автоматическое позиционирование. Функции "Упорядочивание", "Позиционирование по списку" и "Автоматическая расстановка компонентов" помогут легко и быстро оптимизировать расположение компонентов и размеры платы

Эффективные возможности трассировки. Современный бессеточный автотрассировщик способен качественно и быстро разводить как сложные многослойные платы с разными типами компонентов, так и простые двухслойные проекты. Сеточный трассировщик может использоваться на простых однослойных платах с перемычками. Поддержка Specctra DSN/SES позволяет использовать внешние трассировщики. Развитые средства ручной трассировки дают возможность быстро и эффективно проектировать нестандартные платы. Размеры плат неограниченны

Всесторонняя проверка проекта. Широкие возможности проверки проекта на различных этапах создания позволяют выявить ошибки до отправки файлов производителю. Проверка включает следующие этапы: автоматизированная проверка новых компонентов в библиотеках, выявляющая возможные признаки ошибок и минимизирующая "человеческий фактор"; проверка допустимости соединений в схеме (ERC); проверка зазоров, размерностей и различных признаков ошибок на плате (DRC); проверка целостности соединений на плате; сравнение со схемой. Ошибки выводятся в виде списка и отображаются в проекте, возможно их исправление "на лету" с перезапуском проверки

3D предпросмотр платы. Функция трехмерного предпросмотра моделирует внешний вид конечного изделия, дает возможность выявить недостатки компоновки до передачи в производство. Благодаря аппаратному ускорению графики возможно поворачивать и масштабировать модель устройства в реальном времени. С программой поставляются более 2.5 тыс 3D-моделей корпусов

Моделирование схемы. Экспорт принципиальной схемы в формате Spice-нетлист (.cir) даст возможность промоделировать устройство в программе LT Spice или любом другом внешнем симуляторе

Импорт / экспорт. Функции импорта и экспорта позволяют работать с принципиальными схемами, платами и библиотеками в форматах других EDA и CAD-приложений Создание файлов для производства. Можно получить все необходимые для производства файлы (Gerber RS-274X, Excellon N/C Drill, DXF). Векторизация позволяет экспортировать в Gerber-формат TrueType шрифты и растровые изображения

Создание собственных библиотек. Удобные средства разработки компонентов и корпусов с автоматическим расположением и нумерацией выводов по заданным правилам позволяют за считанные минуты создавать компоненты любых размеров и сложности

Редактор плат - проектирование плат с помощью мощного автотрассировщика, удобной ручной трассировки и системы позиционирования компонентов;

Редактор схем - проектирование схем с поддержкой иерархии и неограниченного количества листов. Экспорт в редактор плат, список сетей (netlist) или симулятор;

Редакторы компонентов и корпусов - позволяют создавать свои библиотеки, стандартные библиотеки - содержат более 100 000 компонентов;

3D предпросмотр - позволяет просматривать трехмерную модель платы. С программой поставляются более 2.5 тыс. 3D-моделей корпусов.

Импорт/Экспорт - система может импортировать схемы, платы и библиотеки из P-CAD, PADS и других популярных программ. Экспорт в P-CAD, Gerber и другие форматы позволит подготовить платы для любого производства

Рисунок 3.2 - Компоненты - составляющие редактора DipTrace.

Рисунок 3.3 – Верхний слой печатной платы. Элементы.

Рисунок 3.4 – Верхний слой печатной платы. Проводники.

Рисунок 3.5 - Нижний слой печатной платы. Проводники.

Программа может исполняться пользователем полностью или в пошагово, с трассировкой блоков функций, или выполнением до того места, где стоит курсор. Также существует дополнительная функция определения неограниченного числа точек останова, каждая такая точка может быть подключена или отключена. Точки останова сохраняются между сессиями работы.

Информация о процессе исполнения программы показывается в окне исходного текста.

AVR Studio иметь в своем распоряжении много других окон, которые дают возможность управлять и визуализировать информацию о любом элементе микроконтроллера.

Список доступных окон представлен на рисунке 3.6.

При выходе из редактора AVR Studio настройки рабочего окружения будут сохранены. При первом запуске программы необходимо настроить окна для управления и вывода информации. Эти настройки будут автоматически восстановлены при следующей загрузке.

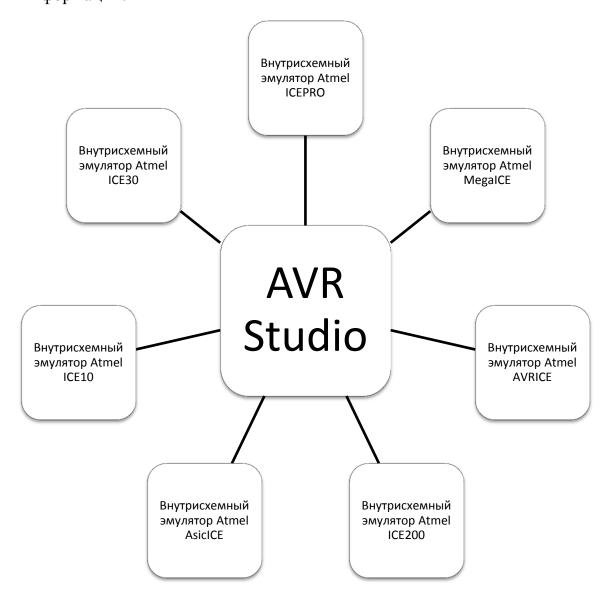

В AVR Studio включена поддержка отладочных средств фирмы Atmel (рисунок 3.7).

Любые программаторы и отладочные средства, поддерживающие микроконтроллеры фирмы Atmel, совместимы с AVR Studio.

Программный код самотестирования модуля представлен в приложении А.

# 3.3 Тестирование и отладка микропроцессорного модуля тестирования

Микропроцессорная система - это система реального времени, правильное ее функционирование зависит от времени выполнения отдельных программ, а также от скорости работы ее компонентов. Таким образом, система будет считаться отлаженной только после того, как рабочие программы правильно функционируют на действительной аппаратуре системы в реальных условиях.

Тенденция развития средств отладки микропроцессорных систем заклю-

чается в объединении свойств нескольких приборов в одном комплексе, в организации унифицированных средств, которые были бы пригодны для автономной отладки аппаратуры, генерации и автономной отладки программ и комплексной отладки системы. Такие комплексы дают возможность проводить разработку и отладку, с постепенным усложнением аппаратуры и программ. Новая, не отлаженная аппаратура и программа внедряются в разрабатываемую систему, добавляются к проверенной ее части.

Watch window: Окно показывает значения определенных символов. В этом окне пользователь может просматривать значения и адреса переменных

Trace window: Окно показывает хронологию программы, выполняемой в настоящее время

Register window: Окно показывает содержимое регистров. Регистры можно изменять во время остановки программы

Memory windows: Окна показывают содержимое памяти программ, данных, портов ввода/вывода и энергонезависимого ПЗУ. Память можно просматривать в НЕХ, двоичном или десятичном форматах. Содержимое памяти можно изменять во время остановки программы

I/O window: Показывает содержимое различных регистров ввода/вывода: EEPROM, I/O порты, таймеры и т.д.

Message window: Окно показывает сообщения от AVR Studio

Processor window: В окне отображается важная информация о ресурсах микроконтроллера, включая программный счетчик, указатель стека, регистр статуса и счетчик цикла. Эти параметры могут модифицироваться во время остановки программы.

Рисунок 3.6 - Список доступных окон AVR Studio.

Средства отладки на последних этапах разработки системы не должны повлиять на правильное функционирование системы, внести задержки и дополнительные нагрузки.

Во время комплексной отладки наравне с детерминированным тестированием применяется статистическое тестирование, при котором МПС тестируется при изменении исходных переменных в соответствии со статистическими законами работы источников информации. Контроль работоспособности проектируемой системы возрастает при этом за счет увеличения диапазона возможных сочетаний переменных и соответствующих им логических маршрутов обработки информации.

Рисунок 3.7 - Отладочные средства фирмы Atmel.

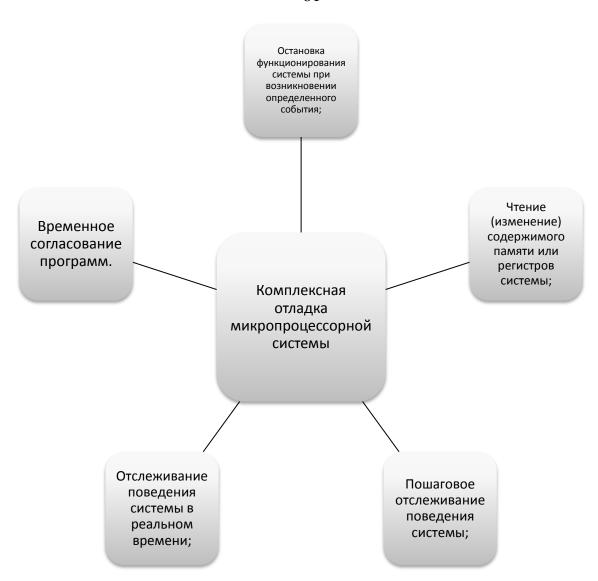

Есть пять основных приемов комплексной отладки микропроцессорной системы, они представлены на рисунке 3.8.

Комплексная отладка заканчивается приемосдаточными испытаниями, подтверждающими соответствие спроектированной системы и технического

задания. При проведении комплексной отладки МПС применяют логические анализаторы и комплексы.

# 3.4 Описание эксплуатационной документации микропроцессорного модуля тестирования

## Назначение модуля

Микропроцессорный модуль тестирования предназначен для тестирования либо управления устройствами на основе микроконтроллеров на правильность исполнения программной составляющей.

Рабочая температура окружающей среды от –10 до плюс 50 C.

### Технические характеристики микропроцессорного модуля:

- а) напряжение питания, 12 В;

- б) потребляемая мощность, не более 120 Вт;

- в) габаритные размеры, 350 х 300 х 80 мм.

Рисунок 3.8 - Комплексная отладка микропроцессорной системы.

### Работа микропроцессорного модуля

На подключенную к микропроцессорному устройству МПС подается питание. Следом следует ввести номер тестируемой системы. После выявления номера тестируемой системы проводится проверка подачи сигнала тестирования, если сигнала нет, то алгоритм заново переходит на стадию установки номера тестируемой системы. Если сигнал «тест» подан, то система определяет адрес подпрограммы тестирования для микросхемы. Следом проводится тестирование микросхемы, с последующим выводом результата на экран. Если сигнал тест к тому моменту все еще поступает, то программа возвращается на стадию определения адреса подпрограммы тестирования. Если сигнал не поступает проводится проверка сигнала сброса. Если сигнал есть, то программа пере-

ходит на стадию выбора номера тестируемой системы. В противном случае идет выключение тестера.

### Установка микропроцессорного модуля

Порядок установки модуля:

- а) закрепить модуль тестирования на специально подготовленной платформе;

- б) в память через программатор вносится управляющая программа;

- в) к отключенному модулю тестирования через интерфейсы подключается устройство для тестирования или управления;

- г) подача сигнала;

- д) выбор алгоритма работы модуля тестирования.

#### Подготовка изделия к использованию

Личный состав должен тщательно изучить назначение и работу каждой составной части изделия и знать назначение всех команд управления.

### Общие указания

Для быстрого обнаружения и устранения неисправностей требуется не только знать устройство и действие изделия, но и уметь правильно определить, где находится неисправность. Неправильное определение неисправности приводит к излишней трате времени и дополнительным работам.

#### Заключение

В результате выполнения бакалаврской работы был спроектирован микропроцессорный модуль тестирования и управления электронными устройствами на базе микропроцессоров. За основу микропроцессорного устройства был взят микроконтроллер AT89C51 семейства MCS. Устройство осуществляет программным путем тестирование либо управление подключаемого прибора.

В процессе выполнения бакалаврской работы был произведен анализ основных проблем тестирования оборудования. Были рассмотрены основные задачи тестирования компонентов микропроцессорных систем: тестирование центрального процессора, тестирования постоянно запоминающих устройств, тестирование устройств с произвольной выборкой, тестирование устройств ввода — вывода. Был проведен анализ основных методов тестирования микропроцессорных систем: программы самоконтроля, тестирование нагрузками, локализация отказов, дерево поиска неисправностей, эмулирующие устройства, системы проектирования. Были выведены основные требования к разрабатываемому устройству.

На этапе проектирования была построена структурная схема модуля. Были выбраны составляющие микропроцессорного модуля, язык программирования, а также подобраны интерфейсы для связи с подключаемым оборудованием. Был разработан алгоритм работы модуля и выполнен подсчет показателя качества создаваемого устройства.

На этапе реализации модуля тестирования была собрана конструкторскотехнологическая документация, описаны процессы компоновки узлов микропроцессорной системы и особенностей программирования. Были описаны способы тестирования и отладки микропроцессорного устройства и создана эксплуатационная документация модуля тестирования электронных устройств.

### Список используемой литературы